This electronic version (PDF) was scanned by the International Telecommunication Union (ITU) Library & Archives Service from an original paper document in the ITU Library & Archives collections.

La présente version électronique (PDF) a été numérisée par le Service de la bibliothèque et des archives de l'Union internationale des télécommunications (UIT) à partir d'un document papier original des collections de ce service.

Esta versión electrónica (PDF) ha sido escaneada por el Servicio de Biblioteca y Archivos de la Unión Internacional de Telecomunicaciones (UIT) a partir de un documento impreso original de las colecciones del Servicio de Biblioteca y Archivos de la UIT.

(ITU) للاتصالات الدولي الاتحاد في والمحفوظات المكتبة قسم أجراه الضوئي بالمسح تصوير نتاج (PDF) الإلكترونية النسخة هذه والمحفوظات المكتبة قسم في المتوفرة الوثائق ضمن أصلية ورقية وثيقة من نقلاً

此电子版(PDF版本)由国际电信联盟(ITU)图书馆和档案室利用存于该处的纸质文件扫描提供。

Настоящий электронный вариант (PDF) был подготовлен в библиотечно-архивной службе Международного союза электросвязи путем сканирования исходного документа в бумажной форме из библиотечно-архивной службы МСЭ.

# INTERNATIONAL TELECOMMUNICATION UNION

CCITT THE INTERNATIONAL TELEGRAPH AND TELEPHONE CONSULTATIVE COMMITTEE

# **BLUE BOOK**

VOLUME VIII - FASCICLE VIII.1

# DATA COMMUNICATION OVER THE TELEPHONE NETWORK

# SERIES V RECOMMENDATIONS

# IXTH PLENARY ASSEMBLY

MELBOURNE, 14-25 NOVEMBER 1988

Geneva 1989

# **COVERING NOTE**

### GENERAL SECRETARIAT INTERNATIONAL TELECOMMUNICATION UNION

### Subject : ERRATA SHEET FOR BLUE BOOK VERSION RECOMMENDATION V.42

Geneva, August 1990

FASCICLE VIII.1

IXth PLENARY ASSEMBLY OF THE CCITT MELBOURNE, 1988

Following the publication of Volume VIII, Fascicle VIII.1 of the *Blue Book*, technical experts in Study Group XVII discovered a number of editorial discrepancies in the text of Recommendation V.42. Some of these would lead to improper implementation if the text were precisely followed. The technical experts have developed and submitted to the CCITT a comprehensive list of the necessary corrections. While these will be reflected in the published text at some future date, printing deadlines did not permit their inclusion in the present version. The reader is kindly requested to take note of the errata noted below while considering the content of Recommendation V.42 (only the technically significant corrections are noted in this document).

Table 8/V.42 (page 317): Within the Supervisory format, second line, change "RR" (above "Receive not Ready") to "RNR" in two places (concerns F/E versions only).

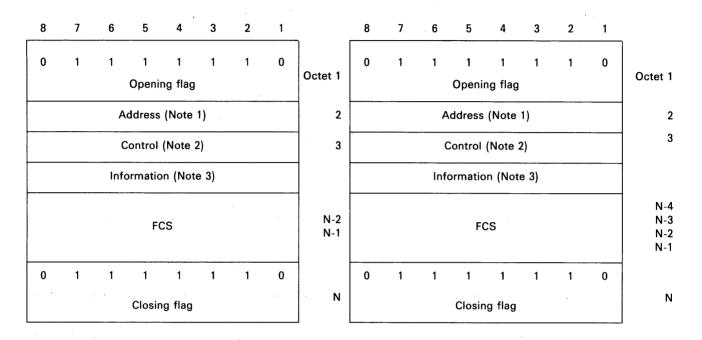

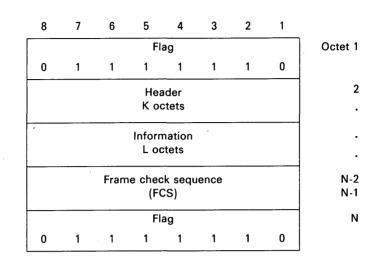

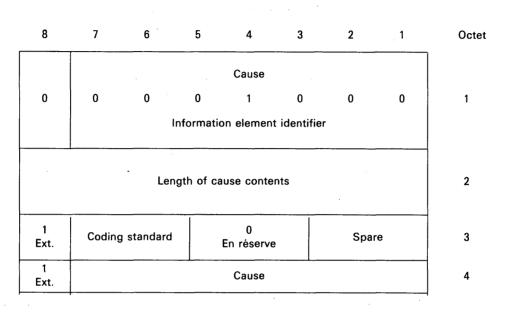

Figure 9/V.42: Decrease all octet numbers by 1 (in the table and throughout the text of the notes).

Section 8.4.3.2 (page 323): In the last paragraph (bottom of page), change the words "and stop timer T401" to "and start timer T401".

Section 8.4.6, Note 2 (page 326): All of the text beginning with Note 2 and continuing to the heading for § 8.4.7 is part of Note 2 and should be properly indented.

Section 8.5.5 (page 329): Replace the second paragraph with "Upon occurrence of a frame-rejection condition, the error-correcting entity shall initiate re-establishment (see § 8.4.9.2) while an error-corrected condition is established. At other times, the frame causing the condition shall be discarded.

(The following corrections concern English version only.)

Section 8.10.(page 332): Change "T410" to "T401".

Section A.6.6.1.3 (page 353): Change "data-sequence phase" to "data-sequence space".

Section A.7.1.5.6 (page 358): Change "all known parameters" to "all unknown parameters".

Section A.7.2.4 (page 358): In the heading, change "Executive" to "Excessive".

Section A.7.3 (page 358): In the second paragraph, change "transfer data" to "transfer user data".

Section A.7.3.5 (page 360): In the first paragraph, change "have been acknowledged" to "have not been acknowledged". In the last paragraph, change "any unacknowledged LT frames" to "any acknowledged LT frames".

Section A.7.4.5 (page 361): In the heading, change "LA" to "LNA".

Section A.7.5.1 (page 362): In the list of definition of terms in the formula, change " $L_r$ " to " $L_f$ ".

INTERNATIONAL TELECOMMUNICATION UNION

CCITT

THE INTERNATIONAL TELEGRAPH AND TELEPHONE CONSULTATIVE COMMITTEE

**BLUE BOOK**

VOLUME VIII - FASCICLE VIII.1

# DATA COMMUNICATION OVER THE TELEPHONE NETWORK

# SERIES V RECOMMENDATIONS

IXTH PLENARY ASSEMBLY MELBOURNE, 14-25 NOVEMBER 1988

Geneva 1989

ISBN 92-61-03661-9

### Printed in Switzerland

### CONTENTS OF THE CCITT BOOK APPLICABLE AFTER THE NINTH PLENARY ASSEMBLY (1988)

,

### **BLUE BOOK**

| Volume I       |                                                                                                                                                                         |

|----------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FASCICLE I.1   | - Minutes and reports of the Plenary Assembly.                                                                                                                          |

|                | List of Study Groups and Questions under study.                                                                                                                         |

| FASCICLE I.2   | - Opinions and Resolutions.                                                                                                                                             |

|                | Recommendations on the organization and working procedures of CCITT (Series A).                                                                                         |

| FASCICLE I.3   | - Terms and definitions. Abbreviations and acronyms. Recommendations on means of expression (Series B) and General telecommunications statistics (Series C).            |

| FASCICLE I.4   | - Index of Blue Book.                                                                                                                                                   |

| Volume II      |                                                                                                                                                                         |

| FASCICLE II.1  | - General tariff principles - Charging and accounting in international telecommunications services. Series D Recommendations (Study Group III).                         |

| FASCICLE II.2  | <ul> <li>Telephone network and ISDN – Operation, numbering, routing and mobile service.</li> <li>Recommendations E.100-E.333 (Study Group II).</li> </ul>               |

| FASCICLE II.3  | <ul> <li>Telephone network and ISDN – Quality of service, network management and traffic<br/>engineering. Recommendations E.401-E.880 (Study Group II).</li> </ul>      |

| FASCICLE II.4  | - Telegraph and mobile services - Operations and quality of service. Recommenda-<br>tions F.1-F.140 (Study Group I).                                                    |

| FASCICLE II.5  | - Telematic, data transmission and teleconference services - Operations and quality of service. Recommendations F.160-F.353, F.600, F.601, F.710-F.730 (Study Group I). |

| FASCICLE II.6  | <ul> <li>Message handling and directory services – Operations and definition of service. Recommendations F.400-F.422, F.500 (Study Group I).</li> </ul>                 |

| Volume III     |                                                                                                                                                                         |

| FASCICLE III.1 | - General characteristics of international telephone connections and circuits. Recommenda-<br>tions G.100-G.181 (Study Groups XII and XV).                              |

| FASCICLE III.2 | - International analogue carrier systems. Recommendations G.211-G.544 (Study Group XV).                                                                                 |

| FASCICLE III.3 | - Transmission media - Characteristics. Recommendations G.601-G.654 (Study Group XV).                                                                                   |

| FASCICLE III.4 | - General aspects of digital transmission systems; terminal equipments. Recommenda-<br>tions G.700-G.795 (Study Groups XV and XVIII).                                   |

| FASCICLE III.5 | <ul> <li>Digital networks, digital sections and digital line systems. Recommendations G.801-G.961<br/>(Study Groups XV and XVIII).</li> </ul>                           |

| FASCICLE III.6 | <ul> <li>Line transmission of non-telephone signals. Transmission of sound-programme and televi-<br/>sion signals. Series H and J Recommendations (Study Group XV).</li> </ul>                                                                                                     |

|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FASCICLE III.7 | <ul> <li>Integrated Services Digital Network (ISDN) – General structure and service capabilities.<br/>Recommendations I.110-I.257 (Study Group XVIII).</li> </ul>                                                                                                                  |

| FASCICLE III.8 | <ul> <li>Integrated Services Digital Network (ISDN) – Overall network aspects and functions,<br/>ISDN user-network interfaces. Recommendations I.310-I.470 (Study Group XVIII).</li> </ul>                                                                                         |

| FASCICLE III.9 | <ul> <li>Integrated Services Digital Network (ISDN) – Internetwork interfaces and maintenance<br/>principles. Recommendations I.500-I.605 (Study Group XVIII).</li> </ul>                                                                                                          |

| Volume IV      |                                                                                                                                                                                                                                                                                    |

| FASCICLE IV.1  | - General maintenance principles: maintenance of international transmission systems and telephone circuits. Recommendations M.10-M.782 (Study Group IV).                                                                                                                           |

| FASCICLE IV.2  | <ul> <li>Maintenance of international telegraph, phototelegraph and leased circuits. Maintenance of<br/>the international public telephone network. Maintenance of maritime satellite and data<br/>transmission systems. Recommendations M.800-M.1375 (Study Group IV).</li> </ul> |

| FASCICLE IV.3  | <ul> <li>Maintenance of international sound-programme and television transmission circuits.<br/>Series N Recommendations (Study Group IV).</li> </ul>                                                                                                                              |

| FASCICLE IV.4  | - Specifications for measuring equipment. Series O Recommendations (Study Group IV).                                                                                                                                                                                               |

| Volume V       | - Telephone transmission quality. Series P Recommendations (Study Group XII).                                                                                                                                                                                                      |

| Volume VI      |                                                                                                                                                                                                                                                                                    |

| FASCICLE VI.1  | - General Recommendations on telephone switching and signalling. Functions and informa-<br>tion flows for services in the ISDN. Supplements. Recommendations Q.1-Q.118 <i>bis</i> (Study<br>Group XI).                                                                             |

| FASCICLE VI.2  | - Specifications of Signalling Systems Nos. 4 and 5. Recommendations Q.120-Q.180 (Study Group XI).                                                                                                                                                                                 |

| FASCICLE VI.3  | <ul> <li>Specifications of Signalling System No. 6. Recommendations Q.251-Q.300 (Study Group XI).</li> </ul>                                                                                                                                                                       |

| FASCICLE VI.4  | <ul> <li>Specifications of Signalling Systems R1 and R2. Recommendations Q.310-Q.490 (Study<br/>Group XI).</li> </ul>                                                                                                                                                              |

| FASCICLE VI.5  | - Digital local, transit, combined and international exchanges in integrated digital networks and mixed analogue-digital networks. Supplements. Recommendations Q.500-Q.554 (Study Group XI).                                                                                      |

| FASCICLE VI.6  | - Interworking of signalling systems. Recommendations Q.601-Q.699 (Study Group XI).                                                                                                                                                                                                |

| FASCICLE VI.7  | <ul> <li>Specifications of Signalling System No. 7. Recommendations Q.700-Q.716 (Study<br/>Group XI).</li> </ul>                                                                                                                                                                   |

| FASCICLE VI.8  | <ul> <li>Specifications of Signalling System No. 7. Recommendations Q.721-Q.766 (Study<br/>Group XI).</li> </ul>                                                                                                                                                                   |

| FASCICLE VI.9  | - Specifications of Signalling System No. 7. Recommendations Q.771-Q.795 (Study Group XI).                                                                                                                                                                                         |

| FASCICLE VI.10 | - Digital subscriber signalling system No. 1 (DSS 1), data link layer. Recommendations Q.920-Q.921 (Study Group XI).                                                                                                                                                               |

- FASCICLE VI.11 Digital subscriber signalling system No. 1 (DSS 1), network layer, user-network management. Recommendations Q.930-Q.940 (Study Group XI).

- FASCICLE VI.12 Public land mobile network. Interworking with ISDN and PSTN. Recommendations Q.1000-Q.1032 (Study Group XI).

- FASCICLE VI.13 Public land mobile network. Mobile application part and interfaces. Recommendations Q.1051-Q.1063 (Study Group XI).

- FASCICLE VI.14 Interworking with satellite mobile systems. Recommendations Q.1100-Q.1152 (Study Group XI).

- Volume VII

- FASCICLE VII.1 Telegraph transmission. Series R Recommendations. Telegraph services terminal equipment. Series S Recommendations (Study Group IX).

- FASCICLE VII.2 Telegraph switching. Series U Recommendations (Study Group IX).

- FASCICLE VII.3 Terminal equipment and protocols for telematic services. Recommendations T.0-T.63 (Study Group VIII).

- FASCICLE VII.4 Conformance testing procedures for the Teletex Recommendations. Recommendation T.64 (Study Group VIII).

- FASCICLE VII.5 Terminal equipment and protocols for telematic services. Recommendations T.65-T.101, T.150-T.390 (Study Group VIII).

- FASCICLE VII.6 Terminal equipment and protocols for telematic services. Recommendations T.400-T.418 (Study Group VIII).

- FASCICLE VII.7 Terminal equipment and protocols for telematic services. Recommendations T.431-T.564 (Study Group VIII).

### Volume VIII

- FASCICLE VIII.1 Data communication over the telephone network. Series V Recommendations (Study Group XVII).

- FASCICLE VIII.2 Data communication networks: services and facilities, interfaces. Recommendations X.1-X.32 (Study Group VII).

- FASCICLE VIII.3 Data communication networks: transmission, signalling and switching, network aspects, maintenance and administrative arrangements. Recommendations X.40-X.181 (Study Group VII).

- FASCICLE VIII.4 Data communication networks: Open Systems Interconnection (OSI) Model and notation, service definition. Recommendations X.200-X.219 (Study Group VII).

- FASCICLE VIII.5 Data communication networks: Open Systems Interconnection (OSI) Protocol specifications, conformance testing. Recommendations X.220-X.290 (Study Group VII).

- FASCICLE VIII.6 Data communication networks: interworking between networks, mobile data transmission systems, internetwork management. Recommendations X.300-X.370 (Study Group VII).

- FASCICLE VIII.7 Data communication networks: message handling systems. Recommendations X.400-X.420 (Study Group VII).

- FASCICLE VIII.8 Data communication networks: directory. Recommendations X.500-X.521 (Study Group VII).

- Volume IX Protection against interference. Series K Recommendations (Study Group V). Construction, installation and protection of cable and other elements of outside plant. Series L Recommendations (Study Group VI).

v

### Volume X

| FASCICLE X.1 | <ul> <li>Functional Specification and Description Language (SDL). Criteria for using Formal<br/>Description Techniques (FDTs). Recommendation Z.100 and Annexes A, B, C and E,<br/>Recommendation Z.110 (Study Group X).</li> </ul> |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| FASCICLE X.2 | - Annex D to Recommendation Z.100: SDL user guidelines (Study Group X).                                                                                                                                                             |

| FASCICLE X.3 | - Annex F.1 to Recommendation Z.100: SDL formal definition. Introduction (Study Group X).                                                                                                                                           |

| FASCICLE X.4 | - Annex F.2 to Recommendation Z.100: SDL formal definition. Static semantics (Study Group X).                                                                                                                                       |

| FASCICLE X.5 | - Annex F.3 to Recommendation Z.100: SDL formal definition. Dynamic semantics (Study Group X).                                                                                                                                      |

| FASCICLE X.6 | - CCITT High Level Language (CHILL). Recommendation Z.200 (Study Group X).                                                                                                                                                          |

| FASCICLE X.7 | - Man-Machine Language (MML). Recommendations Z.301-Z.341 (Study Group X).                                                                                                                                                          |

### CONTENTS OF FASCICLE VIII.1 OF THE BLUE BOOK

### Series V Recommendations

### Data communication over the telephone network

.

| Rec. No.    |                                                                                                                                                                     | Page |

|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

| A.20        | Collaboration with other international organizations over data transmission                                                                                         | 3    |

| SECTION 1 – | General                                                                                                                                                             | •    |

| V.1         | Equivalence between binary notation symbols and the significant conditions of a two-condition code                                                                  | 5    |

| V.2         | Power levels for data transmission over telephone lines                                                                                                             | 7    |

| V.4         | General structure of signals of international alphabet No. 5 code for character oriented data transmission over public telephone networks                           | 9    |

| <b>V</b> .5 | Standardization of data signalling rates for synchronous data transmission in the general switched telephone network                                                | 11   |

| V.6         | Standardization of data signalling rates for synchronous data transmission on leased telephone-type circuits                                                        | 11   |

| V.7         | Definitions of terms concerning data communication over the telephone network                                                                                       | 12   |

| SECTION 2 - | Interfaces and voice-band modems                                                                                                                                    |      |

| V.10        | Electrical characteristics for unbalanced double-current interchange circuits for general use with integrated circuit equipment in the field of data communications | 15   |

| V.11        | Electrical characteristics for balanced double-current interchange circuits for general use with integrated circuit equipment in the field of data communications   | 32   |

| V.13        | Simulated carrier control                                                                                                                                           | 44   |

| V.14        | Transmission of start-stop characters over synchronous bearer channels                                                                                              | 45   |

| V.15        | Use of acoustic coupling for data transmission                                                                                                                      | 49   |

| V.16        | Medical analogue data transmission modems                                                                                                                           | 50   |

| V.19        | Modems for parallel data transmission using telephone signalling frequencies                                                                                        | 56   |

Fascicle VIII.1 - Table of Contents VII

VIII

Fascicle VIII.1 - Table of Contents

| V.20            | Parallel data transmission modems standardized for universal use in the general switched telephone network                                                                                                                           | 60  |

|-----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| V.21            | 300 bits per second duplex modem standardized for use in the general switched telephone network                                                                                                                                      | 65  |

| V.22            | 1200 bits per second duplex modem standardized for use in the general switched telephone network and on point-to-point 2-wire leased telephone-type circuits                                                                         | 69  |

| <b>V.22</b> bis | 2400 bits per second duplex modem using the frequency division technique standar-<br>dized for use on the general switched telephone network and on point-to-point 2-wire<br>leased telephone-type circuits                          | 82  |

| V.23            | 600/1200-baud modem standardized for use in the general switched telephone network                                                                                                                                                   | 98  |

| V.24            | List of definitions for interchange circuits between data terminal equipment (DTE) and data circuit-terminating equipment (DCE)                                                                                                      | 104 |

| V.25            | Automatic answering equipment and/or parallel automatic calling equipment on the general switched telephone network including procedures for disabling of echo control devices for both manually and automatically established calls | 121 |

| V.25 bis        | Automatic calling and/or answering equipment on the general switched telephone network (GSTN) using the 100-series interchange circuits                                                                                              | 131 |

| V.26            | 2400 bits per second modem standardized for use on 4-wire leased telephone-type circuits                                                                                                                                             | 153 |

| V.26 <i>bis</i> | 2400/1200 bits per second modem standardized for use in the general switched telephone network                                                                                                                                       | 158 |

| V.26 ter        | 2400 bits per second duplex modem using the echo cancellation technique standardized for use on the general switched telephone network and on point-to-point 2-wire leased telephone-type circuits                                   | 165 |

| V.27            | 4800 bits per second modem with manual equalizer standardized for use on leased telephone-type circuits                                                                                                                              | 181 |

| V.27 <i>bis</i> | 4800/2400 bits per second modem with automatic equalizer standardized for use on leased telephone-type circuits                                                                                                                      | 187 |

| V.27 ter        | 4800/2400 bits per second modem standardized for use in the general switched telephone network                                                                                                                                       | 199 |

| V.28            | Electrical characteristics for unbalanced double-current interchange circuits                                                                                                                                                        | 211 |

| V.29            | 9600 bits per second modem standardized for use on point-to-point 4-wire leased telephone-type circuits                                                                                                                              | 215 |

| V.31            | Electrical characteristics for single-current interchange circuits controlled by contact closure                                                                                                                                     | 228 |

| V:31 bis        | Electrical characteristics for single-current interchange circuits using optocouplers                                                                                                                                                | 231 |

| V.32            | A family of 2-wire, duplex modems operating at data signalling rates of up to 9600 bit/s for use on the general switched telephone network and on leased telephone-type circuits                                                     | 234 |

| V.33            | 14 400 bits per second modem standardized for use on point-to-point 4-wire leased telephone-type circuits                                                                                                                            | 252 |

Rec. No.

|             |                                                                                                                           | 80  |

|-------------|---------------------------------------------------------------------------------------------------------------------------|-----|

| SECTION 3 – | Wideband modems                                                                                                           |     |

| V.35        | Data transmission at 48 kilobits per second using 60-108 kHz group band circuits                                          | 267 |

| V.36        | Modems for synchronous data transmission using 60-108 kHz group band circuits                                             | 267 |

| V.37        | Synchronous data transmission at a data signalling rate higher than 72 kbit/s using 60-108 kHz group band circuits        | 276 |

| SECTION 4 – | Error control                                                                                                             |     |

| V.40        | Error indication with electromechanical equipment                                                                         | 287 |

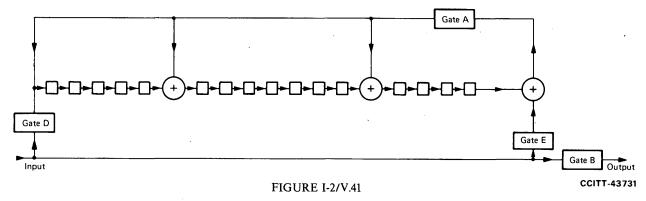

| V.41        | Code-independent error-control system                                                                                     | 287 |

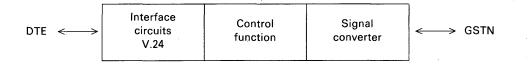

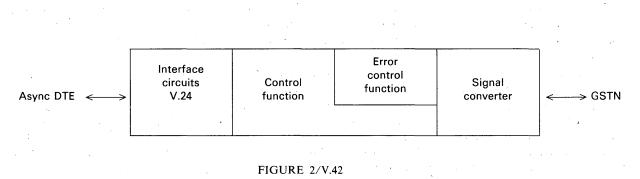

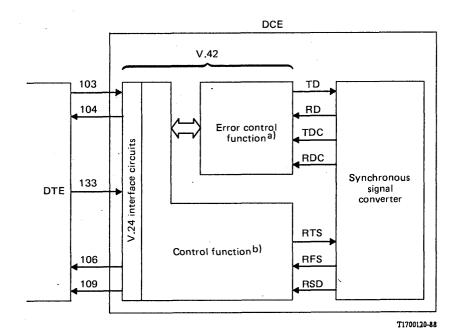

| V.42        | Error-correcting procedures for DCES using asynchronous-to-synchronous conversion .                                       | 296 |

| SECTION 5 – | Transmission quality and maintenance                                                                                      |     |

| V.50        | Standard limits for transmission quality of data transmission                                                             | 371 |

| V.51        | Organization of the maintenance of international telephone-type circuits used for data transmission                       | 372 |

| V.52        | Characteristics of distortion and error-rate measuring apparatus for data transmission .                                  | 372 |

| V.53        | Limits for the maintenance of telephone-type circuits used for data transmission                                          | 372 |

| V.54        | Loop test devices for modems                                                                                              | 375 |

| V.55        | Specification for an impulsive noise measuring instrument for telephone-type circuits .                                   | 392 |

| V.56        | Comparative tests of modems for use over telephone-type circuits                                                          | 392 |

| V.57        | Comprehensive data test set for high data signalling rates                                                                | 400 |

| SECTION 6 – | Interworking with other networks                                                                                          |     |

| V.100       | Interconnection between public data networks (PDNs) and the public switched tele-<br>phone networks (PSTN)                | 401 |

| V.110       | Support of data terminal equipments (DTEs) with V-series type interfaces by an integrated services digital network (ISDN) | 406 |

| V.120       | Support by an ISDN of data terminal equipment with V-series type interfaces with provision for statistical multiplexing   | 453 |

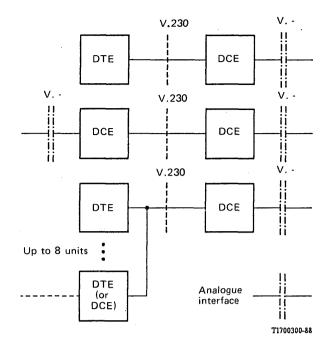

| V.230       | General data communications interface layer 1 specification                                                               | 478 |

|             |                                                                                                                           |     |

1 The Questions entrusted to each Study Group for the Study Period 1989-1992 can be found in Contribution No. 1 to that Study Group.

2 In this Volume, the expression "Administration" is used for shortness to indicate both a telecommunication Administration and a recognized private operating agency.

3 The status of annexes and appendices attached to the Series V Recommendations should be interpreted as follows:

- an annex to a Recommendation forms an integral part of the Recommendation;

÷...

- an *appendix* to a Recommendation does not form part of the Recommendation and only provides some complementary explanation or information specific to that Recommendation.

X Fascicle VIII.1 – Table of Contents

# FASCICLE VIII.1

## Series V Recommendations

# DATA COMMUNICATION OVER THE TELEPHONE NETWORK

# PAGE INTENTIONALLY LEFT BLANK

# PAGE LAISSEE EN BLANC INTENTIONNELLEMENT

### PRINCIPLES GOVERNING THE COLLABORATION BETWEEN THE CCITT AND OTHER INTERNATIONAL ORGANIZATIONS IN THE STUDY OF DATA COMMUNICATIONS

Recommendation A.20 published in Volume I is reproduced below for the convenience of the reader of the Series V Recommendations.

**Recommendation A.20**

### COLLABORATION WITH OTHER INTERNATIONAL ORGANIZATIONS OVER DATA TRANSMISSION

(Geneva, 1964; amended at Mar del Plata, 1968, and at Geneva, 1972, 1976 and 1980; Malaga-Torremolinos, 1984)

### The CCITT,

### considering

(a) that, according to Article 1 of the agreement between the United Nations and the International Telecommunication Union, the United Nations recognizes the International Telecommunication Union as the specialized agency responsible for taking such action as may be appropriate under its basic instrument for the accomplishment of the purposes set forth therein;

(b) that Article 4 of the International Telecommunication Convention (Nairobi, 1982) states that the purposes of the Union are:

- "a) to maintain and extend international cooperation between all Members of the Union for the improvement and rational use of telecommunications of all kinds, as well as to promote and to offer technical assistance to developing countries in the field of telecommunications;

- b) to promote the development of technical facilities and their most efficient operation with a view to improving the efficiency of telecommunication services, increasing their usefulness and making them, so far as possible, generally available to the public;

- c) to harmonize the actions of nations in the attainment of those ends;"

(c) that Article 40 of the Convention states that, in furtherance of complete international coordination on matters affecting telecommunication, the Union shall cooperate with international organizations having related interests and activities;

(d) that in the study of data transmission the CCITT has to collaborate with the organizations dealing with data processing and office equipment and particularly the International Organization for Standardization (ISO) and the International Electrotechnical Commission (IEC);

(e) that this collaboration has to be organized in a manner that will avoid duplication of work and decisions that would be contrary to the principles set out above;

3

### unanimously declares the view

that international standards for data transmission should be established with the following considerations in mind:

(1) Clearly it will be the responsibility of the CCITT to lay down standards for *transmission channels*, i.e. aspects of data transmission which require a knowledge of telecommunication networks or affect performance of these networks.

(2) The standardization of signal conversion terminal equipment (modems) is the province of the CCITT; the standardization of the junction (interface) between modem and the data terminal equipment is a matter of agreement between the CCITT and the ISO or the IEC.

- (3) Devices designed to detect and (or) correct errors must take account of:

- the error rate tolerable to the user;

- the line transmission conditions;

- the code, which has to meet the exigencies of the data alphabet and the requirements of error control (this must be such as to give an output satisfactory to the user) together with the requisite signalling (synchronism, repetition signals, etc.).

Standardization here may not come wholly within the CCITT's province, but the CCITT has very considerable interests at stake.

(4) The alphabet (as defined in Fascicle X.1 - Terms and Definitions) is a "table of correspondence between an agreed set of characters and the signals which represent them".

The CCITT and the ISO reached agreement on an alphabet for general (but not exclusive) use for data and message transmission and have standardized a common alphabet which is known as International Alphabet No. 5 (CCITT Recommendation T.50 and ISO Standard No. 646-1983; ISO 7-bit coded character set for information interchange).

Complementary study of some control characters of the alphabet should be effected cooperatively.

(5) Coding (as defined in Fascicle X.1 - Terms and Definitions) is "a system of rules and conventions according to which the telegraph signals forming a message or the data signals forming a block should be formed, transmitted, received and processed". Hence, it consists of a transformation of the format of the signals in the alphabet for taking account of synchronous methods, and introduction of redundancy in accordance with the error control system. This is not a field in which the CCITT alone may be able to decide; however, no decision should be taken without reference to the Committee, because of the possible restrictions which transmission and switching peculiarities may impose on coding.

When the general switched network is used (telephone or telex) and when the error control devices are subject to restrictions (switching signals – reserved sequences), it is the CCITT which is in fact responsible for any necessary standardization in conjunction with other bodies.

(6) The limits to be observed for transmission performance on the transmission path (modem included) fall within the competence of the CCITT; the limits for the transmission performance of the sending equipment and the margin of terminal data equipment (depending on the terminal apparatus and the transmission path limits) should be fixed by agreement between the ISO and the CCITT.

(7) In all instances, the CCITT alone can lay down manual and automatic operating procedures for the setting-up, holding and clearing of calls for data communications when the general switched networks are used, including type and form of signals to be interchanged at the interface between data terminal equipment and data circuit terminating equipment.

(8) When a public data network is involved, the CCITT has the responsibility to provide the Recommendations which apply. Where these Recommendations have an impact on the basic design and features of data processing systems and office equipment [normally the Data Terminal Equipment (DTE)], they shall be the subject of consultation between CCITT and ISO and in some cases a mutual agreement may be desirable. Likewise when the ISO is developing or changing standards that may affect compatibility with the public data network there shall be consultation with the CCITT.

### **SECTION 1**

### GENERAL

**Recommendation V.1**

### EQUIVALENCE BETWEEN BINARY NOTATION SYMBOLS AND THE SIGNIFICANT CONDITIONS OF A TWO-CONDITION CODE

(New Delhi, 1960; amended at Geneva, 1964 and 1972)

Binary numbering expresses numbers by means of two digits normally represented by the symbols 0 and 1. Transmission channels are especially well suited to the transmission of signals by a modulation having two significant conditions (two-condition modulation). These two significant conditions are sometimes called "space" and "mark" or "start" and "stop", or they may be called condition A or condition Z [1].

It is very useful to make the two conditions of a two-condition modulation correspond to the binary digits 0 and 1. Such equivalence will facilitate the transmission of numbers resulting from binary calculation, the conversion of codes for binary numbers and of codes for decimal numbers, maintenance operations and relations between transmission personnel and the personnel in charge of data-processing machines.

At first sight, it does not seem to matter whether the symbol 0 corresponds in transmission to condition A or condition Z, the symbol 1 then corresponding to condition Z or condition A or vice versa.

In telegraphy, however, when a telegraphic communication is set up and the sending of signals is stopped (called the idle condition of the line), the signal sent over the line consists of condition Z throughout the suspension of transmission.

It is logical (and for certain VF telegraph systems also essential) to use the same rule in data transmission. During the "idle periods" of transmission, condition Z should be applied to the circuit input.

Data transmission on a circuit is often controlled by perforated tape. On perforated tapes used for telegraphy, condition Z is represented by perforation. When binary numbers are represented by means of perforations, it is customary to represent the symbol 1 by a perforation. It is therefore logical to make this symbol 1 correspond to condition Z.

For these reasons, the CCITT

### unanimously declares the following view:

1 In transmitting data by two-condition code, in which the digits are formed using binary notation, the symbol 1 of the binary notation will be equivalent to condition Z of the modulation, and the symbol 0 of the binary notation will be equivalent to condition A of the modulation.

2 During periods when there is no signal sent to the input of the circuit, the circuit input condition is condition Z.

If perforation is used, one perforation corresponds to one unit interval under condition Z.

4 In accordance with Recommendation R.31, the sending of symbol 1 (condition Z) corresponds to the tone being sent on a channel using amplitude modulation.

5 In accordance with Recommendation R.35, when frequency modulation is used, the sending of symbol 0 corresponds to the higher frequency, while the sending of symbol 1 corresponds to the lower frequency.

a) For phase modulation with reference phase:

the symbol 1 corresponds to a phase equal to the reference phase;

the symbol 0 corresponds to a phase opposed to the reference phase.

b) For differential two-phase modulation where the alternative phase changes are 0 degree or 180 degrees:

the symbol 1 corresponds to a phase inversion from the previous element;

the symbol 0 corresponds to a no-phase inversion from the previous element.

7 A summary of equivalence is shown in Table 1/V.1.

### TABLE 1/V.1

### Summary of equivalence (see Note 1)

|                                                                                                            | Digit 0                                                                                                                                  | Digit 1                                                                                                                                    |

|------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|

|                                                                                                            | "Start" signal in start-stop code<br>Line available condition<br>in telex switching<br>"Space" element of start-stop code<br>Condition A | "Stop" signal in start-stop code<br>Line idle condition<br>in telex switching (Note 2)<br>"Mark" element of start-stop code<br>Condition Z |

| Amplitude modulation                                                                                       | Tone-off                                                                                                                                 | Tone-on                                                                                                                                    |

| Frequency modulation                                                                                       | High frequency                                                                                                                           | Low frequency                                                                                                                              |

| Phase modulation with reference phase                                                                      | Opposite phase to the reference phase                                                                                                    | Reference phase                                                                                                                            |

| Differential two-phase<br>modulation where the<br>alternative phase changes<br>are 0 degree or 180 degrees | No phase inversion                                                                                                                       | Inversion of the phase                                                                                                                     |

| Perforations                                                                                               | No perforation                                                                                                                           | Perforation                                                                                                                                |

Note 1 – The standardization described in this Recommendation is general, whether over telegraph-type circuits or over circuits of the telephone type, making use of electromechanical or electronic devices.

Note 2 – It primarily applies to anisochronous use.

### Reference

[1] CCITT Definition: Position A; position Z, Vol. X, (Terms and Definitions).

6 Fascicle VIII.1 – Rec. V.1

3

6

### POWER LEVELS FOR DATA TRANSMISSION OVER TELEPHONE LINES

### (New Delhi, 1960; amended at Geneva, 1964 and 1980)

The objectives in specifying data signal levels are as follows:

- a) To ensure satisfactory transmission and to permit coordination with devices such as signalling receivers or echo suppressors, the data signal levels on international circuits should be controlled as closely as possible,

- b) To ensure correct performance of multichannel carrier systems from the point of view of loading and noise, the mean power of data circuits should not differ much from the conventional value of channel loading (-15 dBm0 for each direction of transmission: see Note below). This conventional value makes allowance for a reasonable proportion P (dependent on the transmission systems and probably less than 50%; the value will have to be specified in subsequent studies) of the channels in a multichannel system being used for nonspeech applications at fixed power levels at about -13 dBm0 for each direction.

If the proportion of nonspeech applications (including data) does not exceed the above value P, the mean power of -13 dBm0 for each direction of transmission would be allowable for data transmission also.

However, assuming that the proportion of nonspeech circuits is appreciably higher than P (due to the development of data transmission) on international carrier systems, a reduction of this power by 2 dB might be reasonable (these values require further study).

Note – The distribution of long-term mean power among the channels in a multichannel carrier telephone system (conventional mean value of -15 dBm0), probably has a standard deviation in the neighbourhood of 4 dB (see [2]).

- c) It is probable that Administrations will wish to fix specific values for the signal power level of data modulators either at the subscriber's line terminals or at the local exchanges. The relation between these values and the power levels on international circuits depends on the particular national transmission plan; in any case, a wide range of losses among the possible connections between the subscriber and the input to international circuits must be expected.

- d) Considerations a) to c) suggest that specification of the maximum data signal level only is not the most useful form. One alternative proposal would be to specify the nominal power at the input to the international circuit. The nominal power would be the statistically estimated mean power obtained from measurement on many data transmission circuits.

For these reasons, the CCITT

unanimously declares the following view:

### 1 Data transmission over leased telephone circuits (private wires) set up on carrier systems

1.1 The maximum power output of the subscriber's equipment into the line shall not exceed 1 mW at any frequency.

1.2 For systems transmitting tones continuously, e.g., frequency-modulation systems, the maximum power level at the zero relative level point shall be -13 dBm0. When transmission of data is discontinued for any appreciable time, the power level should preferably be reduced to -20 dBm0 or lower.

7

<sup>&</sup>lt;sup>1)</sup> Recommendation V.2 corresponds to Recommendation H.15 [1].

1.3 For systems not transmitting tones continuously, e.g., amplitude-modulation systems, the signal characteristics should meet all of the following requirements:

- i) The maximum value of the 1-minute mean power shall not exceed -13 dBm0.

- ii) Provisionally, the maximum value of the instantaneous power shall not exceed a level corresponding to that of a 0 dBm0 sine wave signal. This limit should be confirmed or amended after further study.

- iii) Provisionally, the maximum signal power determined for a 10-Hz bandwidth centred at any frequency shall not exceed -10 dBm0. This limit should be confirmed or amended after further study.

Note 1 – It is estimated that the proportion of international circuits which are carrying data transmissions is approximately 20%. If the proportion should reach a high level (approximately 50% or even less in the case of high-usage systems), the limits now proposed would need to be reconsidered.

Note 2 – Supplement No. 16 [3] of the Yellow Book, Volume III, gives information on the out-of-band power of signals applied to leased telephone-type circuits.

### 2 Data transmission over the switched telephone system

2.1 The maximum power output of the subscriber's equipment into the line shall not exceed 1 mW at any frequency.

2.2 For systems transmitting tones continuously, such as frequency- or phase-modulation systems, the power level of the subscriber's equipment should be fixed at the time of installation to allow for loss between his equipment and the point of entry to an international circuit, so that the corresponding nominal level of the signal at the international circuit input shall not exceed -13 dBm0.

2.3 For systems not transmitting tones continously, e.g. amplitude-modulation systems, the signal characteristics should meet all of the following requirements (see also Note 1 to § 1.3):

- i) The maximum value of the 1-minute mean power shall not exceed -13 dBm0.

- ii) Provisionally, the maximum value of the instantaneous power shall not exceed a level corresponding to that of a 0 dBm0 sine wave signal. This limit should be confirmed or amended after further study.

- iii) Provisionally, the maximum signal power determined for a 10 Hz bandwidth centred at any frequency shall not exceed -10 dBm0. This limit should be confirmed or amended after further study.

Note 1 – In practice, it is no easy matter to assess the loss between a subscriber's equipment and the international circuit, so that § 2 of the present Recommendation should be taken as providing general planning guidance.

Note 2 - In switched connections, the loss between subscribers' telephones may be high: 30 to 40 dB. The level of the signals received will then be very low, and these signals may suffer disturbance from the dialling pulses sent over other circuits.

If there is likely to be a heavy demand for international connections for data transmission over the switched network, some Administrations might want to provide special 4-wire subscriber lines. If so, the levels to be used might be those proposed for leased circuits.

### References

[1] CCITT Recommendation Power levels for data transmission over telephone lines, Vol. III, Rec. H.51.

[2] Measurement of the load of telephone circuits, Green Book, Vol. III-2, Supplement No. 5, ITU, Geneva, 1973.

- [3] Out-of-band characteristics of signals applied to leased telephone-type circuits, Vol. III, Supplement No. 16.

- 8 Fascicle VIII.1 Rec. V.2

### GENERAL STRUCTURE OF SIGNALS OF INTERNATIONAL ALPHABET No. 5 CODE FOR CHARACTER ORIENTED DATA TRANSMISSION OVER PUBLIC TELEPHONE NETWORKS<sup>1</sup>)

(Mar del Plata, 1968; amended at Geneva, 1976 and 1980, and at Melbourne, 1988)

The CCITT,

### I. considering, firstly,

the agreement between the International Organization for Standardization (ISO) and the CCITT on the main characteristics of a seven-unit alphabet [International Alphabet No. 5 (IA5)] to be used for data transmission and for telecommunications requirements that cannot be met by the existing five-unit International Telegraph Alphabet No. 2 (ITA2);

the interest, both to the users and to the telecommunication services, of an agreement concerning the chronological order of transmission of bits in serial working;

### declares the view

that the agreed rank number of the unit in the alphabetical table of combinations should correspond to the chronological order of transmission in serial working on telecommunication circuits;

that, when this rank in the combination represents the order of the bit in binary numbering, the bits should be transmitted in serial working with the low order bit first;

that the numerical meaning corresponding to each information unit considered in isolation is that of the digit:

0 for a unit corresponding to condition A (travail = space), and

1 for a unit corresponding to condition Z (repos = mark),

in accordance with the definitions of these conditions for a two-condition transmission system;

### II. considering, moreover,

that it is often desirable, in character oriented data transmission, to add an extra "parity" unit to allow for the detection of errors in received signals;

the possibility offered by this addition for the detection of faults in data terminal equipment;

the need to reserve the possibility of making this addition during the transmission itself, after the seven information units proper have been sent;

### declares the view

that signals of the International Alphabet No. 5 code for data transmission should, in general, include an additional "parity" unit;

that the rank of this unit and, hence, the chronological order of the transmission in serial working should be the eighth of the combination thus completed;

### III. considering

that, in start-stop systems working with electromechanical equipment, the margin of such equipment and the reliability of the connection are considerably increased by the use of a stop element corresponding to the duration of two unit intervals of the modulation;

that for transmissions over telephone circuits via modems installed on the user's premises, the latter must be able to use the connections at the highest possible practical rate in characters per second, and that in such a case a single-unit stop element leads to a gain of about 10% as regards this practical rate;

9

<sup>&</sup>lt;sup>1)</sup> See Recommendation X.4 [1] for data transmission over public data networks.

that, however, it does not appear that the production of electronic devices capable of working at will with start-stop signals having a stop element equal to one or two unit intervals should lead to costly complications and that such an arrangement can have the advantage of appreciably limiting the error rate without greatly reducing the practical efficiency of the connection;

### declares the view

that in start-stop systems using combinations of the seven-unit alphabet normally followed by a parity unit, the first information unit of the transmitted combination should be preceded by a start element corresponding to condition A (space);

that the duration of this start element should be a one-unit interval for the modulation rate under consideration, at transmitter output;

that the combination of seven information units, normally completed by its parity unit, should be followed by a stop element corresponding to condition Z (mark);

that for start-stop systems using the seven-unit code on switched telephone networks, a two-unit stop element should be used with electromechanical data terminal equipments operating at modulation rates up to and including 200 bauds. In other cases, the use of a one-unit stop element is preferable. However, this is subject to a mutual agreement between Administrations concerned;

that similar situations when a one-unit stop element can be used may apply to leased circuits;

that the start-stop receivers should be capable of correctly receiving start-stop signals comprising a single-unit stop element, whose duration will be reduced by a time interval equal to the deviation corresponding to the degree of gross start-stop distortion permitted at receiver input. However, for electromechanical equipment which must use a two-unit stop element (eleven-unit code signal) with a modulation rate of 200 bauds or less, receivers should be capable of correctly receiving signals with a stop element reduced to one unit;

### IV. considering, finally,

that the direction of the parity unit can only be that of the even parity on the perforated tapes, particularly owing to the possibility of deletion (combination 7/15 of the alphabet) which causes a hole to appear in all tracks;

that, on the other hand, the odd parity is considered essential in the equipment which depends on transitions in the signals to maintain synchronism [in cases where combination 1/6 (SYNC) of the alphabet does not permit of an economical solution];

### declares the view

that the parity unit of the signal should correspond to the even parity in links or connections operated on the principle of the start-stop system;

that this parity should be odd on links or connections using end-to-end character oriented synchronous operation;

that arrangements should be made when necessary to reverse the direction of the parity unit at the input and output of the synchronous equipment connected either to apparatus working on the start-stop principle or receiving characters on perforated tape;

that the detection of a character out-of-parity may be represented by:

- a) reverse question mark (?) graphic character or a representation of the capital letters SB (see ISO 2047) provided that these letters occupy a single character position on the screen or printer, and could have been entered by a single key stroke, recognizing it may be difficult to achieve a legible "SB" character from some matrix printers or displays where the characters are printed; or

- b) a recording of the 1/10 (SUB) character on the tape or other storage medium, where provided

and that, where a SUB character occurs in a received transmission, or is presented to a DTE via a storage medium, e.g. paper tape, then the reaction should be as in a) and b) above.

### Reference

[1] CCITT Recommendation General structure of signals of International Alphabet No. 5 code for character oriented data transmission over public data networks, Vol. VIII, Rec. X.4.

### STANDARDIZATION OF DATA SIGNALLING RATES FOR SYNCHRONOUS DATA TRANSMISSION IN THE GENERAL SWITCHED TELEPHONE NETWORK

### (former Recommendation V.22, Geneva, 1964; amended at Mar del Plata, 1968, at Geneva, 1972 and 1976, at Malaga-Torremolinos, 1984 and at Melbourne, 1988)

1 Data transmission by international communications carried on the general switched telephone network using a synchronous transmission procedure will be done with a specific mode of modulation, two- or multi-condition, and serial transmission (see Note 1). For synchronous data transmission on leased telephone-type circuits see Recommendation V.6.

2 The data signalling rates for synchronous transmission in the general switched telephone network will be: 600, 1200, 2400, 4800 and 9600 bits (see Note 2).

The users will choose among these rates, in accordance with their needs and the facilities afforded by the connection.

3 Data signalling rates should in no case deviate from the nominal value by more than  $\pm 0.01\%$ .

Note 1 - The application of parallel data transmission is a subject of other Recommendations.

Note 2 – Modems for use in the general switched telephone network at these data signalling rates; see Recommendations V.23, V.26 *bis* and V.27 *ter* respectively for a half-duplex mode of operation, and V.22, V.22 *bis*, V.26 *ter* and V.32, respectively, for a duplex-mode of operation.

Note 3 - For asynchronous data transmission at 300 bit/s, see Recommendation V.21.

### **Recommendation V.6**

### STANDARDIZATION OF DATA SIGNALLING RATES FOR SYNCHRONOUS DATA TRANSMISSION ON LEASED TELEPHONE-TYPE CIRCUITS

(former Recommendation V.22 bis, Geneva, 1972; amended at Geneva, 1976, at Malaga-Torremolinos, 1984 and at Melbourne, 1988)

1 Data transmission by international communications carried on leased telephone-type circuits (either normal quality or special quality circuits) using a synchronous transmission procedure will be done with a specific mode of modulation, two- or multi-condition, and serial transmission (see Note 1). For synchronous data transmission in the general switched telephone network see Recommendation V.5.

2 It is recommended that for synchronous transmission the data signalling rates should be divided into two distinct classes to be known as "preferred" and "supplementary", both of which are included in the "permitted" data signalling rates.

| a) | Preferred range of data signalling rates (bits per second) |                         |  |

|----|------------------------------------------------------------|-------------------------|--|

|    | 600 (see Note 2)                                           | 4 800 (see Note 2)      |  |

|    | 1 200 (see Note 2)                                         | 9 600 (see Note 2)      |  |

|    | 2 400 (see Note 2)                                         | 14 400 (see Note 2)     |  |

| b) | Supplementary range of data signalling                     | rates (bits per second) |  |

| 3 000 (see Note 3) | 7 200 (see Note 2) |

|--------------------|--------------------|

| 5 000 (See Mole 5) | 7 200 (See Note 2) |

6 000 (see Note 3) 12 000 (see Note 3)

c) Permitted range of data signalling rates (bits per second) The range is defined as 600 times "N" bits per second where  $1 \le N \le 24$ ; N: a positive integer. In determining the permitted range, the CCITT has in mind the need to restrict the number of data signalling rates (and hence modem design required), yet at the same time to allow the best use to be made of technical progress in both modem development and improvement in the telephone plant. It is considered that a geometric progression in standard rates provides the most satisfactory basis of development.

3 Data signalling rates should in no case deviate from the nominal value by more than  $\pm 0.01\%$ .

Note 1 - The application of parallel data transmission is a subject of other Recommendations.

Note 2 – Modems for use on leased telephone-type circuits at these data signalling rates; see Recommendations V.22, V.22 bis, V.23, V.26, V.26 ter, V.27, V.27 bis, V.29, V.32 and V.33.

Note 3 – It is recognized that there is a usage of these data signalling rates for the connection of DTEs to circuit switched public data networks. Addition of other data signalling rates for this purpose is under consideration.

Note 4 – Modems for use on leased telephone-type circuits at these signalling rates are under study.

### **Recommendation V.7**

### DEFINITIONS OF TERMS CONCERNING DATA COMMUNICATION OVER THE TELEPHONE NETWORK

(Geneva, 1980; amended at Malaga-Torremolinos, 1984 and at Melbourne, 1988)

Note – This Recommendation contains only new and amended definitions of terms concerning data communication over the telephone network which were elaborated by Study Group XVII since 1977 and approved by the VIIth and VIIIth Plenary Assemblies of the CCITT.

It should be noted that there exist a large number of relevant definitions in force which have been published in the *List of definitions of essential telecommunication terms*, Part I (including its two Supplements), *Green Book*, Volume VIII and *Orange Book*, Volume VIII.2.

### 1 effective data transfer rate

F: débit effectif du transfert des données

S: velocidad real de transferencia de datos

The average number of bits, characters, or blocks per unit time transferred from a data source to a data sink and accepted as valid. It is expressed in bits, characters, or blocks per second, minute, or hour.

### 2 error control

F: contrôle des erreurs

S: control de errores (protección contra errores)

That part of a protocol controlling the detection and possibly the correction of transmission errors.

### 3 data concentrator

- F: concentrateur de données

- S: concentrador de datos

Equipment that permits a common transmission medium to serve more *data sources* than there are data channels currently available within the transmission medium.

12 Fascicle VIII.1 – Rec. V.7

#### simple multipoint circuit 4

- F: circuit multipoint simple

- S: circuito multipunto simple

A multipoint circuit that does not contain more than two DCEs in series and that provides for centralized multipoint operation.

#### 5 inband signalling

F: signalisation dans la bande

S: señalización dentro de banda

The exchange of control signals between interconnected DCEs using the DCE line signal band with which data in the forward channel are transmitted. The transmission of DTE data, if any, is disrupted.

#### out-of-band signalling 6

- F: signalisation hors bande

- S: señalización fuera de banda

The exchange of control signals between interconnected DCEs using signals other than those for the transmission of data in the forward channel. The transmission of DTE data is not disrupted.

#### 7 coded inband signalling

F: signalisation dans la bande avec codage

S: señalización codificada dentro de banda

Inband signalling by which control signals are exchanged via data in the forward channel.

#### 8 half-duplex operation

F: exploitation en semi-duplex

S: explotación (o funcionamiento) semidúplex

The exchange of data in either direction, one direction at a time.

#### 9 interface rate

- F: débit à l'interface

- S: velocidad de interfaz

The transfer rate of the bit stream found on the physical interchange circuits.

#### 10 information rate

- F: débit d'information

- S: velocidad de información

The transfer of information bits (the equivalent of the bit rate of circuit 103 or 104 on a V.24 interface).

#### control signalling rate 11

F: débit de la signalisation de commande

S: velocidad de señalización de control

The transfer rate of the encoded and multiplexed control signalling (the equivalent of V.24 and V.25 interchange circuits, except the data and timing circuits, insofar as required for an application, with the possibility of adding other signalling).

### 12 parallel automatic calling

### F: appel automatique en parallèle

### S: llamada automática paralelo; llamada automática en modo paralelo

A procedure by which a DTE, by use of the 200 series interchange circuits, may instruct a DCE to perform the call establishment function. The transmission, from DTE to DCE, of each digit to be dialled is achieved in parallel form on interchange circuits 206 to 209.

### 13 serial automatic calling

F: appel automatique en série

S: llamada automática serie; llamada automática en modo serie

A procedure by which a DTE, by use of the 100 series interchange circuits, may instruct a DCE to perform the call establishment function. The transmission from DTE to DCE, of each digit to be dialled, is achieved in serial form on interchange circuit 103.

### 14 start-stop transmission

F: transmission arythmique

S: transmisión arrítmica

A form of anisochronous transmission in which each group of contiguous data units is preceded by a start signal and is terminated by a stop signal.

### **SECTION 2**

### INTERFACES AND VOICE-BAND MODEMS

### **Recommendation V.10**

### ELECTRICAL CHARACTERISTICS FOR UNBALANCED DOUBLE-CURRENT INTERCHANGE CIRCUITS FOR GENERAL USE WITH INTEGRATED CIRCUIT EQUIPMENT IN THE FIELD OF DATA COMMUNICATIONS <sup>1</sup>)

### (Geneva, 1976; amended at Geneva, 1980 and at Melbourne, 1988)

### 1 Introduction

This Recommendation deals with the electrical characteristics of the generator, receiver and interconnecting leads of an unbalanced interchange circuit employing a differential receiver.

In the context of this Recommendation an unbalanced interchange circuit is defined as consisting of an unbalanced generator connected to a receiver by an interconnecting lead and a common return lead.

Annexes and Appendices are provided to give guidance on a number of application aspects as follows:

Annex A Compatibility with other interfaces

Annex B Considerations for coaxial cable applications – V.10 COAXIAL

Appendix I Waveshaping

Appendix II Cable guidelines

*Note* – Generator and load devices meeting the electrical characteristics of this Recommendation need not operate over the entire data signalling rate range specified. They may be designed to operate over narrower ranges to satisfy specific requirements more economically, particularly at lower data signalling rates.

The interconnecting cable is normally not terminated, but the matter of terminating coaxial interconnecting cable is dealt with in Annex B. Where the interchange circuit incorporates the special provisions for coaxial applications with cable termination this shall be referred to as "complying with Recommendation V.10 (COAXIAL)".

Reference measurements are described which may be used to verify certain of the recommended parameters but it is a matter for individual manufacturers to decide what tests are necessary to ensure compliance with the Recommendation.

<sup>&</sup>lt;sup>1)</sup> This Recommendation is also designated as X.26 in the Series X Recommendations.

### 2 Field of application

The electrical characteristics specified in this Recommendation apply to interchange circuits operating with data signalling rates up to 100 kbit/s<sup>2)</sup>, and are intended to be used primarily in Data Terminal Equipment (DTE) and Data Circuit-terminating Equipment (DCE) implemented in integrated circuit technology.

This Recommendation is not intended to apply to equipment implemented in discrete component technology, for which the electrical characteristics covered by Recommendation V.28 are more appropriate.

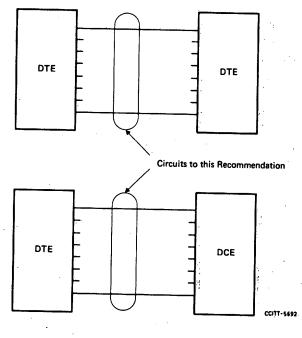

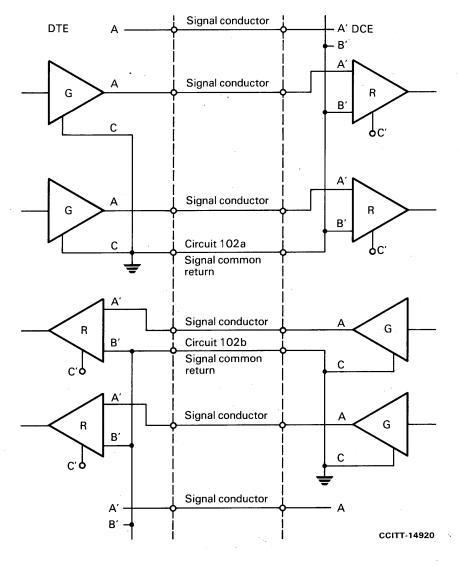

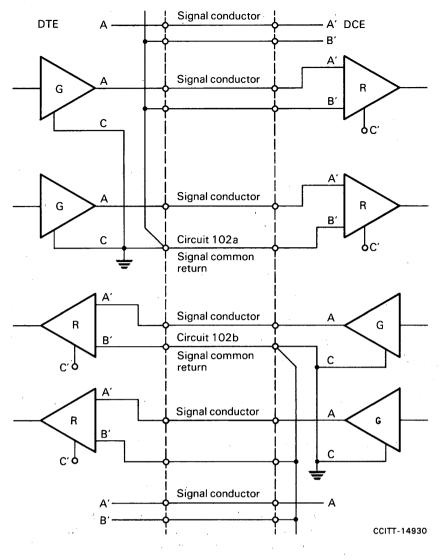

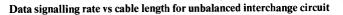

Typical points of application are illustrated in Figure 1/V.10.

### FIGURE 1/V.10

Whilst the unbalanced interchange circuit is primarily intended for use at the lower data signalling rates, its use should be avoided in the following cases:

- 1) where the interconnecting cable is too long for proper unbalanced circuit operation;

- 2) where extraneous noise sources make unbalanced circuit operation impossible;

- 3) where it is necessary to minimize interference with other signals.

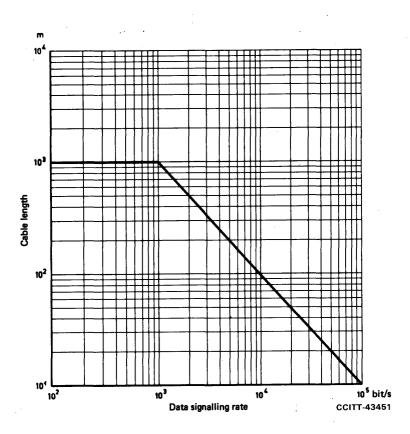

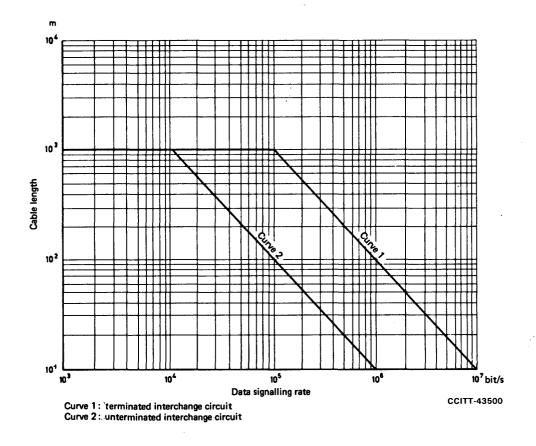

Whilst a restriction on maximum cable length is not specified, guidelines are given with respect to conservative operating distance as a function of data signalling rates (see Appendix II).

<sup>&</sup>lt;sup>2)</sup> Signalling rates above the suggested 100 kbit/s may also be employed, but the maximum suggested operating distances should be shortened accordingly (see Figure II-1/V.10).

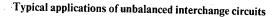

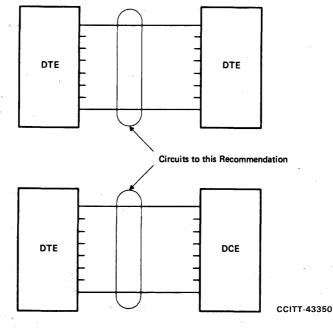

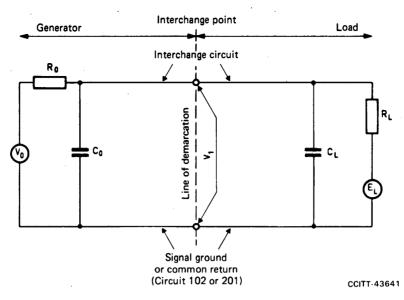

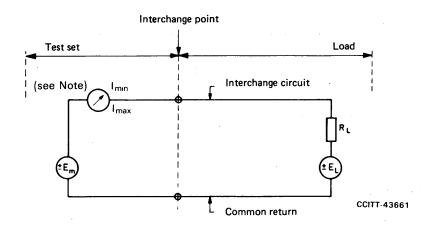

Note I - Two interchange points are shown. The output characteristics of the generator, excluding any interconnecting cable, are defined at the "generator interchange point". The electrical characteristics to which the receiver must respond are defined at the "load interchange point".

Note 2 – The connection of the signal common return is dealt with in § 10 below. Points C and C' may be connected to protective ground if required by national regulations.

Note 3 – The interconnecting cable is normally not terminated. The termination of coaxial interconnecting cable is dealt with in Annex B.

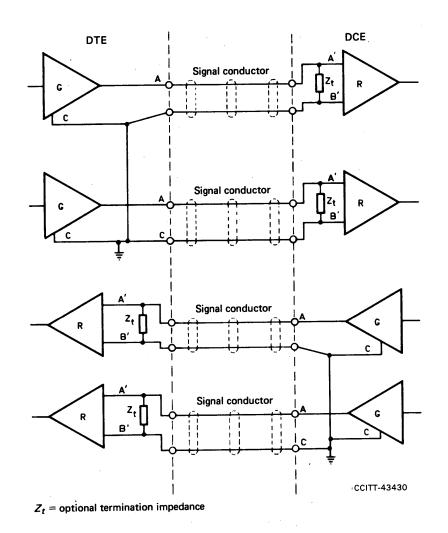

### FIGURE 2/V.10

### Symbolic representation of an unbalanced interchange circuit

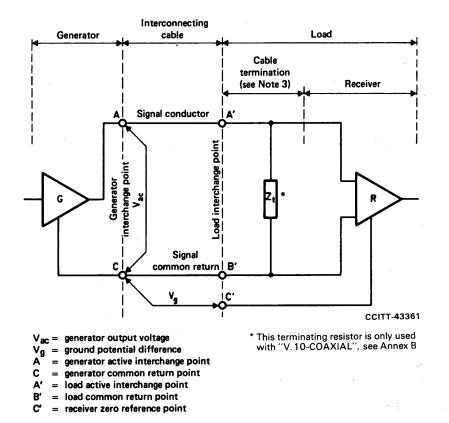

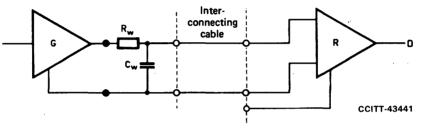

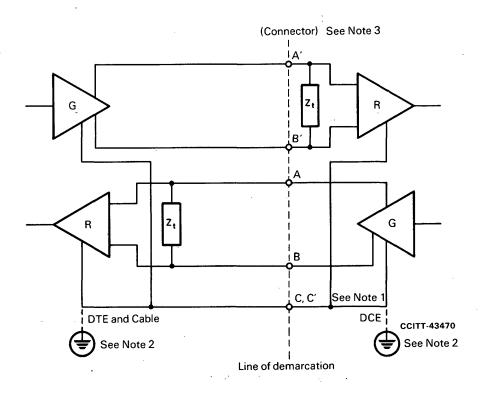

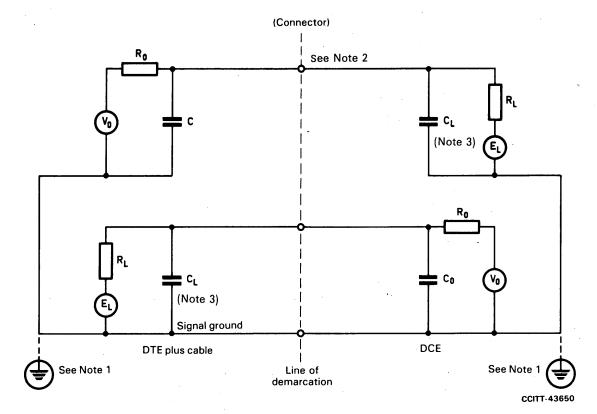

For data transmission applications, it is commonly accepted that the interface cabling is provided by the DTE. This introduces the line of demarcation between the DTE plus cable and the DCE. This line is also called the interchange point and physically implemented in the form of a connector. The applications also require interchange circuits in both directions. This leads to an illustration as shown in Figure 3/V.10.

Note 1 - The zero volt reference interchange points C' may be interconnected via the signal ground conductor. Note 2 - Signal ground may be further connected to external protective ground if national regulations require. Note 3 - The type of connector with this electrical characteristic specification depends on the application. ISO specifies, for data transmission over telephone type facilities, a 37-pin connector in ISO 4902.

### FIGURE 3/V.10

### Practical representation of the interface

### 4 Generator polarities and receiver significant levels

### 4.1 Generator

The signal conditions for the generator are specified in terms of the voltage between output points A and C shown in Figure 2/V.10.

When the signal condition 0 (space) for data circuits, or ON for control and timing circuits, is transmitted the output point A is positive with respect to point C. When the signal condition 1 (mark) for data circuits, or OFF for control and timing circuits, is transmitted the output point A is negative with respect to point C.

۰.

### 4.2 Receiver

The receiver significant levels are shown in Table 1/V.10, where  $V_{A'}$  and  $V_{B'}$  are respectively the voltage at points A' and B' relative to point C'.

### TABLE 1/V.10

### **Receiver significant levels**

|                             | $V_{\mathrm{A}'} - V_{\mathrm{B}'} \leqslant -0.3 \mathrm{V}$ | $V_{\mathrm{A}'} - V_{\mathrm{B}'} \ge +0.3 \mathrm{V}$ |

|-----------------------------|---------------------------------------------------------------|---------------------------------------------------------|

| Data circuits               | 1                                                             | 0                                                       |

| Control and timing circuits | OFF                                                           | ON                                                      |

### 5 Generator<sup>3)</sup>

### 5.1 *Output impedance*

The total dynamic output impedance of the generator shall be equal to or less than 50 ohms.

### 5.2 Static reference measurements

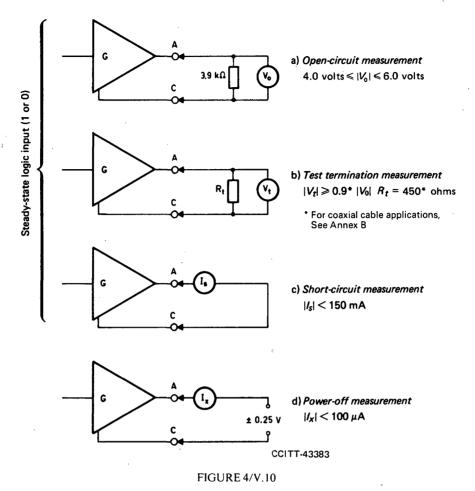

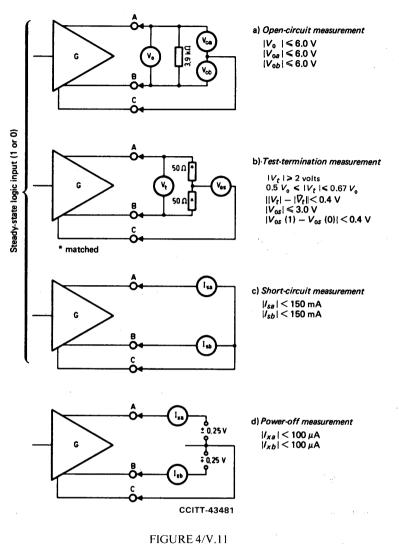

The generator characteristics are specified in accordance with measurements illustrated in Figure 4/V.10 and described in §§ 5.2.1 to 5.2.4 below.

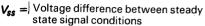

### 5.2.1 Open circuit measurement [Figure 4a)/V.10]

The open circuit voltage measurement is made with a 3900-ohm resistor connected between points A and C. In both binary states, the magnitude of the signal voltage  $(V_0)$  shall be equal to or greater than 4.0 volts but not greater than 6.0 volts.

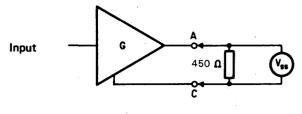

### 5.2.2 Test termination measurement [Figure 4b)/V.10]

With a test load of 450 ohms connected between output points A and C, the magnitude of the output voltage  $(V_i)$  in both binary states shall be equal to or greater than 0.9 of the magnitude of  $V_0$ .

### 5.2.3 Short-circuit measurement [Figure 4c)/V.10]

With the output points A and C short-circuited the current  $(I_s)$  flowing through point A in both binary states shall not exceed 150 milliamperes.

### 5.2.4 Power-off measurements [Figure 4d)/V.10]

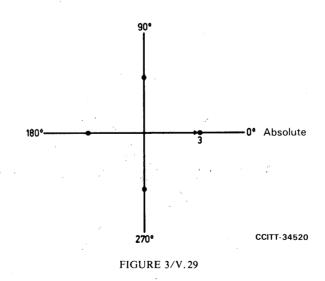

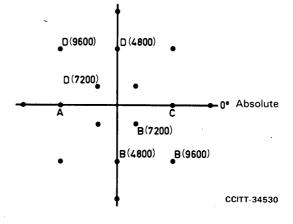

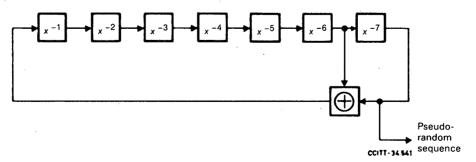

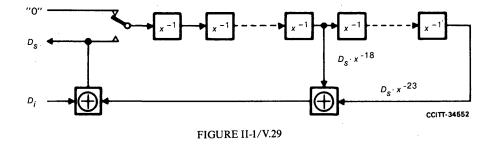

Under power-off condition, with a voltage ranging between +0.25 volt and -0.25 volt applied between the output point A and point C, the magnitude of the output leakage current  $(I_x)$  shall not exceed 100 micro-amperes.